Исследование комбинационных схем

Лабораторная работа выполняется с помощью учебного лабораторного стенда LESO2.

Лабораторная работа выполняется с помощью учебного лабораторного стенда LESO2.

1 Цель работы

Целью работы является изучение принципов действия комбинационных схем: дешифратора, шифратора, преобразователя кода для семисегментного индикатора, мультиплексора, сумматора.

2 Краткие теоретические сведения

2.1 Дешифратор (декодер)

Дешифратор (декодер) служит для преобразования n-разрядного позиционного двоичного кода в единичный выходной сигнал на одном из 2n выходов. При каждой входной комбинации сигналов на одном из выходов появляется 1. Таким образом, по единичному сигналу на одном из выходов можно судить о входной кодовой комбинации. Таблица истинности для декодера с двумя входами изображена в таблице 2.1.

Таблица 2.1 – Таблица истинности двухразрядного дешифратора

| x1 | x2 | y0 | y1 | y2 | y3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

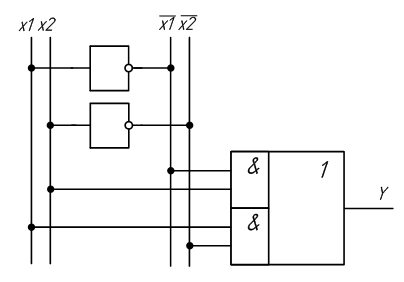

Для построения схемы декодера по таблице истинности воспользуемся методикой, изложенной в лабораторной работе №1, выполняемой на стенде LESO2. Например, устройство должно иметь 4 выхода. Для каждого выхода записываем логическое выражение. На основе СДНФ:

y0 = x1·x2

y1 = x1·x2

y2 = x1·x2

y3 = x1·x2

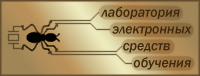

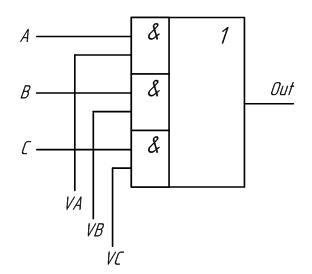

По этой системе выражений несложно построить схему требуемого дешифратора (рисунок 2.1).

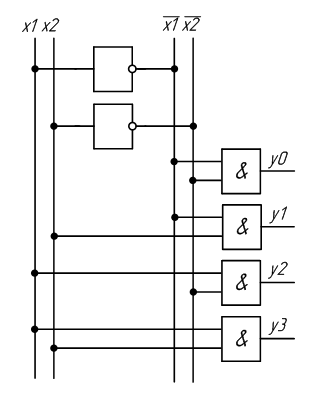

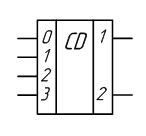

Условное графическое обозначение такого дешифратора изображено на рисунке 2.2.

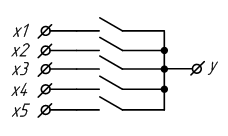

2.2 Шифратор (кодер)

Шифратор выполняет функцию, обратную декодеру (дешифратору), то есть преобразует непозиционный (унитарный) двоичный 2n разрядный код в n разрядный позиционный код. При подаче на один из входов единичного сигнала на выходе формируется соответствующий двоичный код. Составим таблицу истинности шифратора при n = 2.

Таблица 2.2 – Таблица истинности шифратора при n = 2

| x1 | x2 | x3 | x4 | y1 | y0 |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 1 | 1 |

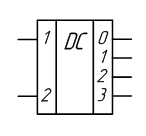

Синтезируем шифратор. Для этого запишем систему его собственных функций:

y1 = x1 · x2 · x3 · x4 + x1 · x2 · x3 ·x4

y0 = x1 · x2 · x3 · x4 + x1 · x2 · x3 ·x4

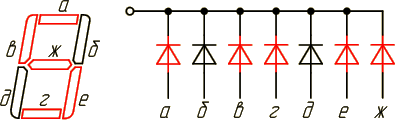

2.3 Преобразователь кода для семисегментного индикатора

Наиболее широко преобразователи кодов известны применительно к цифровым индикаторам. Например, преобразователь 4-х разрядного позиционного двоичного кода в десятичные цифры. Имеется семи сегментный индикатор и с его помощью требуется высветить десять цифр.

Очевидно, что двоичный код должен иметь не менее 4 - х разрядов (2^4 = 16, что больше 10). Составим таблицу истинности работы такого преобразователя.

Таблица 2.3 – Таблица истинности преобразователя

| Цифра | Двоичный код 8-4-2-1 | a | б | в | г | д | е | ж | |||

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

По ТИ несложно составить систему собственных функций для всех выходов, т.е. СДНФ, минимизировать её и составить принципиальную схему.

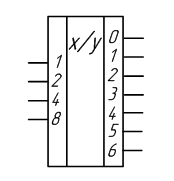

2.4 Мультиплексор

Мультиплексор – устройство, которое позволяет коммутировать один из 2^n информационных входов X на один выход Y под действием n управляющих (адресных) сигналов. На рисунке. 2.7 изображена упрощенная функциональная схема мультиплексора на идеализированных электронных ключах.

В цифровых схемах требуется управлять ключами при помощи логических уровней. Поэтому желательно подобрать устройство, которое могло бы выполнять функции электронного ключа с управлением цифровым сигналом. Попробуем «заставить» работать в качестве электронного ключа уже знакомые нам логические элементы. Рассмотрим ТИ логического элемента «И». При этом один из входов логического элемента «И» будем рассматривать как информационный вход электронного ключа, а другой вход – как управляющий. Так как оба входа логического элемента «И» эквивалентны, то не важно какой из них будет управляющим входом. Пусть вход X будет управляющим, а Y – информационным. Для простоты рассуждений, разделим ТИ на две части в зависимости от уровня логического сигнала на управляющем входе X.

Таблица 2.4 – Таблица истинности

| y | x | Out |

| 0 0 |

0 1 |

0 0 |

| 1 1 |

0 1 |

0 1 |

По таблице истинности отчётливо видно, что если на управляющий вход X подан нулевой логический уровень, сигнал, поданный на вход Y, на выход Out не проходит. При подаче на управляющий вход X логической единицы, сигнал, поступающий на вход Y, появляется на выходе Out. Это означает, что логический элемент «И» можно использовать в качестве электронного ключа. При этом не важно, какой из входов элемента "И" будет использоваться в качестве управляющего входа, а какой – в качестве информационного. Остается только объединить выходы элементов «И» на один общий выход. Это делается при помощи логического элемента «ИЛИ» точно так же как и при построении схемы по произвольной таблице истинности. Получившийся вариант схемы коммутатора с управлением логическими уровнями приведён на рисунке 2.8.

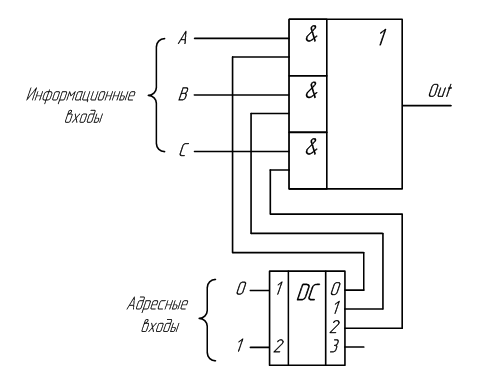

В схемах, приведенных на рисунках 2.7 и 2.8, можно одновременно включать несколько входов на один выход. Однако обычно это приводит к непредсказуемым последствиям. Кроме того, для управления таким коммутатором требуется много входов, поэтому в состав мультиплексора обычно включают двоичный дешифратор, как показано на рисунке 2.9. Такая схема позволяет управлять переключением информационных входов мультиплексора при помощи двоичных кодов, подаваемых на его управляющие входы. Количество информационных входов в таких схемах выбирают кратным степени числа два.

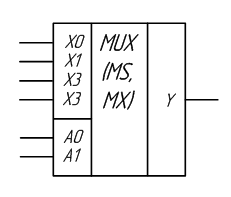

Условное графическое обозначение 4–х входового мультиплексора с управлением двоичным кодом приведено на рисунке 2.10. Входы A0 и A1 являются управляющими входами мультиплексора, определяющими адрес информационного входного сигнала, который будет соединён с выходным выводом мультиплексора Y. Информационные входные сигналы обозначены: X0, X1, X2 и X3.

В условном графическом обозначении названия информационных входов A, B, C и D заменены названиями X0, X1, X2 и X3, а название выхода Out заменено на название Y. Такое обозначение входов и выходов мультиплексора более распространено в отечественной литературе. Адресные входы обозначены как A0 и A1.

Об особенностях реализации мультиплесоров на языке Verilog можно почитать в статье:

Архитектура ПЛИС. Часть 2. Мультиплексор

2.5 Сумматор

Сумматор – узел компьютера, предназначенный для сложения двоичных чисел. Построение двоичных сумматоров обычно начинается с сумматора по модулю 2.

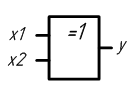

Сумматор по модулю 2

Схема сумматора по модулю 2 совпадает со схемой исключающее «ИЛИ».

Таблица 2.5 – Таблица истинности сумматора по модулю 2

| x1 | x2 | y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Логическое выражение, описывающее сумматор по модулю 2:

y = x1 · x2 + x1 · x2

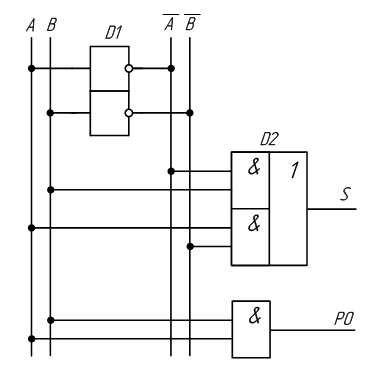

На основе логического уравнения, описывающего этот элемент можно синтезировать схему:

Сумматор по модулю 2 выполняет суммирование без учёта переноса. В обычном двоичном сумматоре требуется учитывать перенос, поэтому требуются схемы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такой схемы, называемой полусумматором, приведена в таблице 2.6.

Таблица 2.6 – Таблица истинности полусумматора

| A | B | S | P0 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Здесь A и B – слагаемые;

S – сумма;

P0 – перенос в старший разряд (выход переноса Pout).

Запишем систему собственных функций для полусумматора:

S = A · B + A · B

P0 = A · B

Полный сумматор.

Схема полусумматора формирует перенос в старший разряд, но не может учитывать перенос из младшего разряда. При сложении многоразрядных двоичных чисел необходимо складывать три цифры в каждом разряде – 2 слагаемых и единицу переноса из предыдущего разряда PI.

Таблица 2.7 – Таблица истинности полного сумматора

| PI | A | B | S | PO |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

PI – вход 1 переноса из предыдущего разряда,

PO – выход 1 переноса в старший разряд.

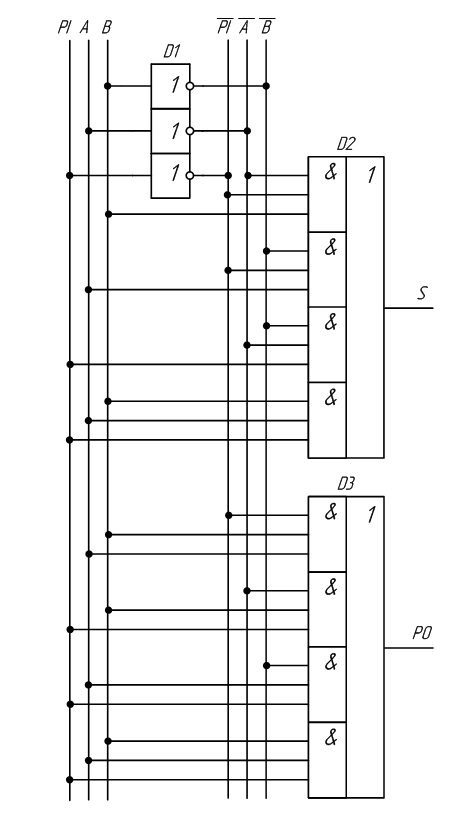

На основании таблицы истинности запишем систему собственных функций для каждого выхода:

S = A · B · PI + A · B · PI + A · B · PI + A · B · PI

PO = A · B · PI + A · B · PI + A · B · PI + A · B · PI

В результате получим схему полного сумматора (рисунок 2.15).

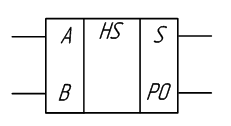

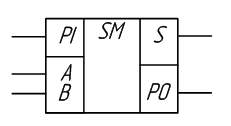

Рисунок 2.16 – Изображение полного двоичного одноразрядного сумматора на схемах

|

Вопросы |

3 Задание к работе

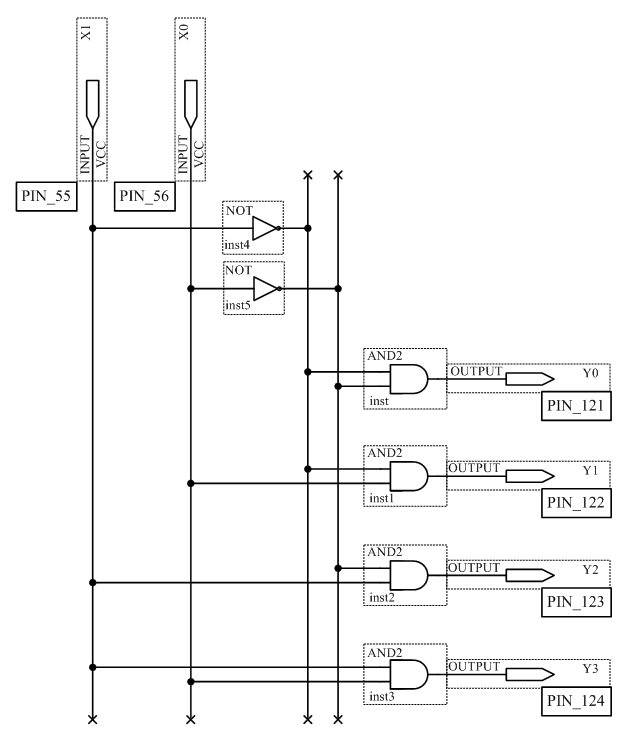

3.1 Исследовать принцип работы дешифратора 2 x 4

Сконфигурировать ПЛИС в соответствии с рисунком 3.1. Подключить к входам X0 и X1 переключатели S7 и S8, а к выходам Y0, Y1, Y2, Y3 светодиодные индикаторы LED5, LED6, LED7, LED8. Для этого подключить входы и выходы дешифратора к соответствующим ножкам ПЛИС.

Подавая все возможные комбинации логических уровней на входы X0, X1 с помощью ключей S7, S8 и наблюдая за состояниями светодиодных индикаторов LED5, LED6, LED7, LED8, заполните таблицу истинности дешифратора.

Таблица 3.1 – Таблица дешифратора

| x1 | x2 | y0 | y1 | y2 | y3 |

| 0 | 0 | ||||

| 0 | 1 | ||||

| 1 | 0 | ||||

| 1 | 1 |

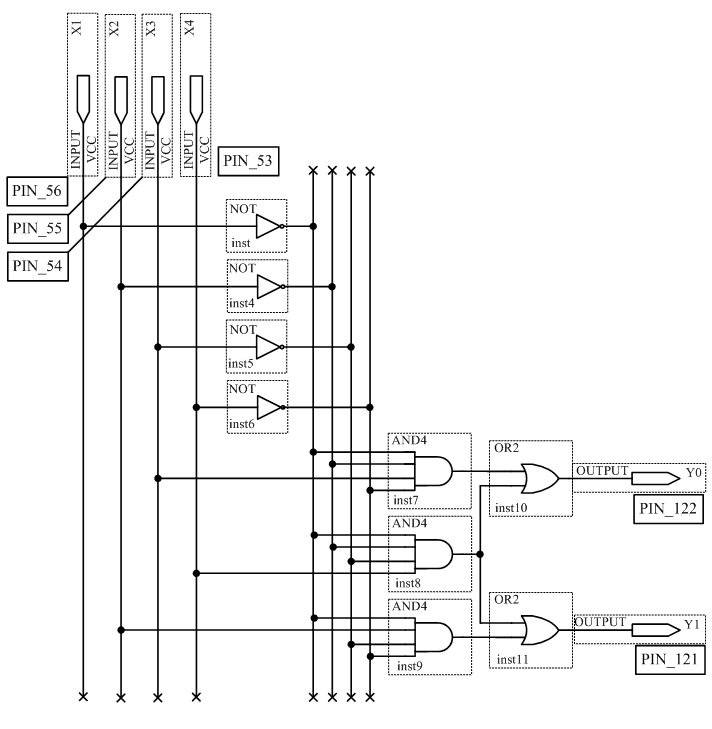

3.2 Исследовать принцип работы шифратора 4x2

Сконфигурировать ПЛИС в соответствии с рисунком 3.2.

Подключить к входам X1, X2, X3, X4 переключатели S8, S7, S6, S5, а к выходам Y0, Y1 светодиодные индикаторы LED8, LED7. Для этого подключить входы и выходы дешифратора к соответствующим ножкам ПЛИС. Подавая все возможные комбинации логических уровней на входы X1, X2, X3, X4 с помощью ключей S8, S7, S6, S5 и наблюдая за состояниями светодиодных индикаторов LED7, LED8, заполните таблицу истинности шифратора.

Таблица 3.2 – Таблица истинности шифратора

| x1 | x2 | x3 | x4 | y1 | y0 |

| 1 | 0 | 0 | 0 | ||

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 0 | 1 |

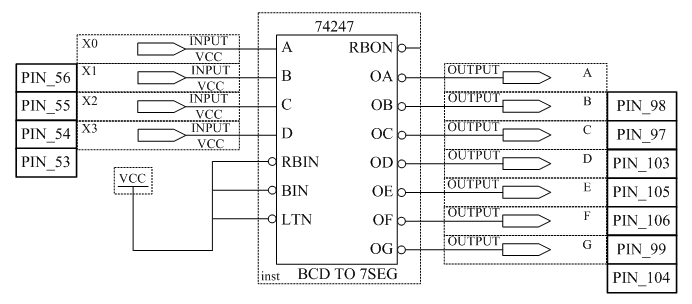

3.3 Исследовать работу преобразователя кода для семисегментного индикатора.

Составить таблицу истинности преобразователя кода (таблица. 3.3).

Собрать схему, изображенную на рисунке 3.3.

Таблица 3.3 – Таблица истинности преобразователя

| x3 | x2 | x1 | x0 | A | B | C | D | E | F | G |

| 0 | 0 | 0 | 0 | |||||||

| 0 | 0 | 0 | 1 | |||||||

| 0 | 0 | 1 | 0 | |||||||

| 0 | 0 | 1 | 1 | |||||||

| 0 | 1 | 0 | 0 | |||||||

| 0 | 1 | 0 | 1 | |||||||

| 0 | 1 | 1 | 0 | |||||||

| 0 | 1 | 1 | 1 | |||||||

| 1 | 0 | 0 | 0 | |||||||

| 1 | 0 | 0 | 1 |

Подавая с помощью ключей S8, S7, S6, S5 различные кодовые комбинации на входы X0, X1, X2, X3 определить цифры, высвечиваемые на индикаторе. По результатам эксперимента заполнить таблицу 3.4.

Таблица 3.4 – Таблица, описывающая работу преобразователя кода для семисегментного индикатора

| x3 | x2 | x1 | x0 | Показание индикатора |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 |

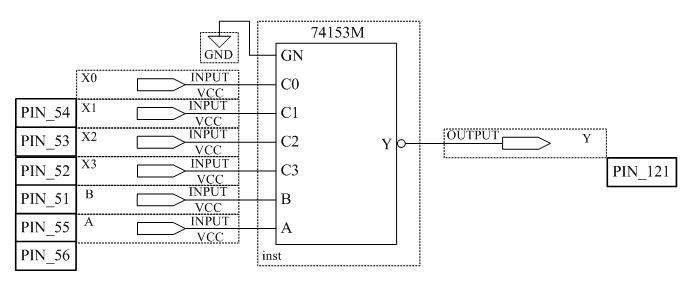

3.4 Исследовать работу мультиплексора 4x1

Сконфигурировать ПЛИС в соответствии с рисунком 3.4.

Поочередно устанавливая все возможные кодовые комбинации на адресных входах A и B, определите номера коммутируемых каналов. Номер коммутируемого канала определяется путем поочерёдного подключения к входам X0, X2, X3, X4 уровня логической единицы и наблюдения за выходом Y. Заполните таблицу 3.5.

Таблица 3.5 – Таблица, описывающая работу мультиплексора

| B | A | Номер коммутируемого канала |

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

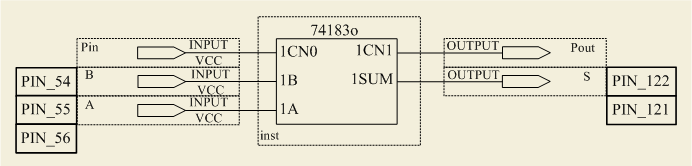

3.5 Исследовать схему сумматора

Сконфигурировать ПЛИС в соответствии с рисунком 3.5. Здесь Pin, Pout соответственно вход и выход единицы переноса, A и B – слагаемые, S – сумма.

Заполнить таблицу истинности сумматора (таблица 3.6).

Таблица 2.7 – Таблица истинности полного сумматора

| Pin | B | A | Pout |

| 0 | 0 | 0 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| 1 | 1 | 1 |

4 Содержание отчета

- Цель работы.

- Схемы исследования дешифратора, шифратора, преобразователя кода для семисегментного индикатора, мультиплексора, сумматора.

- Таблицы истинности для каждой схемы.

- Выводы по каждому заданию.

5 Контрольные вопросы

- Принцип работы дешифратора?

- Как синтезировать дешифратор с произвольной разрядностью?

- Как работает шифратор?

- Изобразите таблицу истинности шифратора.

- Как работает преобразователь кода для семисегментного индикатора?

- Как устроен семи сегментный индикатор?

- Как работает мультиплексор?

- Как в лабораторной работе проводилось исследование мультиплексора?

- Как работает сумматор?

- Изобразите таблицу истинности шифратора.

- Что такое единица переноса?