Методическое указание к лабораторной работе на учебном стенде LESO7.

Шауэрман Александр А. shamrel@yandex.ru

- Цель работы

- Теоретические сведения

- Введение в Verilog

- Ход работы

- Вопросы для самопроверки

- Содержание отчета

1 Цель работы

Изучить алгоритм прямого цифрового синтеза. Изучить реализацию алгоритма на аппаратной платформе ПЛИС. Экспериментально исследовать влияние параметров алгоритма на характеристики сигнала и генератора.

2 Теоретические сведения

2.1 Способы генерации сигналов

Существуют аналоговые способы генерации и цифровые.

Для аналоговых способов генерации сигналов используют автоколебательные системы или автогенератор, принцип которого состоит в том, чтобы энергию от источника питания через управляющий элемент подавать в колебательную систему.

Основные методы цифровой генерации сигналов – метод аппроксимации и табличный метод.

Метод аппроксимации использует представление периодического сигнала в аналитическом виде и выполняет в микропроцессоре вычислений по заданной программе. В памяти устройства хранятся лишь параметры генерируемого сигнала. Программа вычисляет отсчеты функции с некоторым заданным интервалом. При необходимости получения аналогового сигнала далее используется ЦАП. Либо цифровые данные используются внутри устройства, например, в другой программе, или для модуляции. Метод аппроксимации позволяет обходится небольшим объемом памяти. Однако недостатком является необходимость вычисления значительного числа арифметических и логических операций, затрачиваемые на формирование одного отсчета сигнала, что ограничивает максимальную частоту сигнала.

Табличный метод генерации предполагает, что предварительно вычисленные цифровые отсчеты функции постоянно хранятся в памяти. Формирование очередного отсчета сводится к операциям подготовки адреса и чтения соответствующей ячейки памяти. Достоинством этого метода является меньшее время, затрачиваемое на формирование отсчета и, как следствие, возможность генерации сигналов с более высокой частотой. Недостатком является необходимость иметь большой объем памяти данных.

К табличному методу относится метод прямого цифрового синтеза. Прямой цифровой синтез (от англ. DDS – Direct Digital Synthesizer) – метод, позволяющий получить аналоговый сигнал (обычно это синусоидальный сигнал, пилообразный, последовательность треугольных импульсов) за счет генерации временной последовательности цифровых отсчетов и их дальнейшего преобразования в аналоговую форму посредством ЦАП. Так как сигнал сначала синтезируется в цифровой форме, такое устройство может обеспечить быстрое переключение частоты, высокое разрешение по сетке частот, работу в широком диапазоне частот.

2.2 Метод генерации DDS

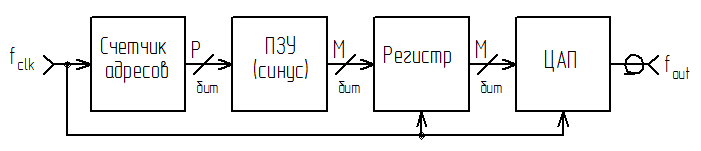

В простейшем случае DDS может быть реализован как счетчик адресов, на которые подаются импульсы с генератора опорной частоты, постоянное запоминающее устройство (ПЗУ) и ЦАП (рисунок 1).

Рисунок 1 – Простейшая функциональная схема DDS

В ПЗУ в цифровом виде хранится полный период гармонического сигнала (синус). ПЗУ в данном случае функционирует как таблица синуса. Счетчик адресов последовательно перебирает все адреса ПЗУ, содержимое ПЗУ через регистр передается на вход ЦАП. ЦАП в свою очередь для каждого слова из ПЗУ генерирует сигнал в аналоговой форме. Выходная частота (fout) такого DDS зависит от двух факторов: во-первых, от опорной частоты fclk , во-вторых, от того, с каким шагом расположены отсчеты синуса в таблице ПЗУ. Хотя у такой простой архитектуры генератора может быть достаточно высокая точность аналогового сигнала и высокая производительность, но ей не хватает гибкости настройки. Частота выходного сигнала может быть изменена только при изменении частоты опорного генератора, либо перепрограммированием ПЗУ.

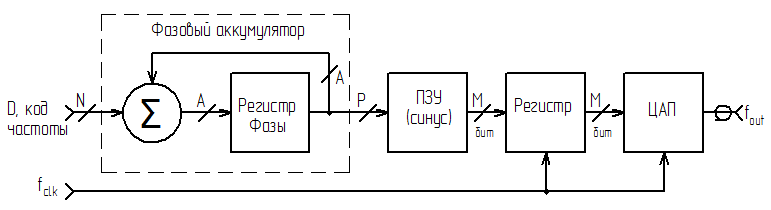

С введением в архитектуру функции фазового аккумулятора ядро DDS получил необходимую гибкость в управлении частотой выходного сигнала. На рисунке 2 показана функциональная схема DDS с фазовым аккумулятором.

Рисунок 2 – Функциональная схема DDS с фазовым аккумулятором

Аккумулятор фазы выполнен по схеме накапливающего сумматора и представляет собой регистр, который в каждом такте работы устройства перезагружается величиной, равной старому содержимому, плюс некоторая постоянная добавка – N разрядный код частоты D. Содержимое регистра линейно увеличивается во времени, только теперь приращение не всегда является единичным, а зависит от величины постоянной добавки.

На вход адресов ПЗУ поступают не все значения регистра фазы, а только P старших разрядов. Данный механизм называется «усечение фазы» и будет рассмотрен позже.

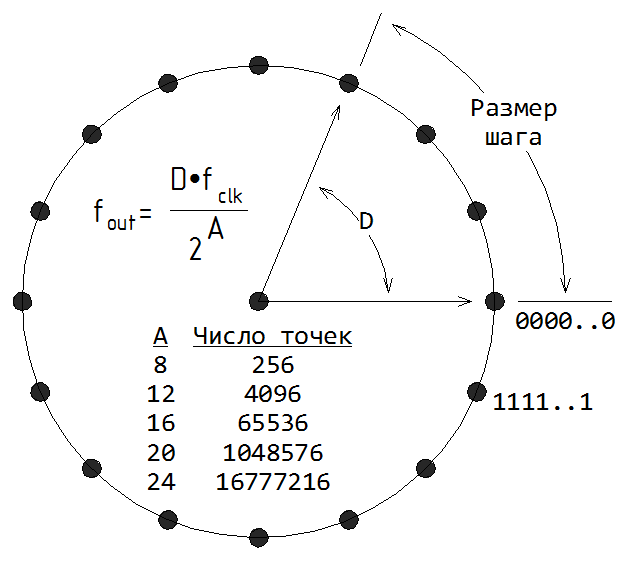

Функционирование фазового аккумулятора может быть показано с помощью круговой диаграммы (рисунок 3).

Рисунок 3 – Круговая диаграмма фазового аккумулятору

Каждая точка на круговой диаграмме соответствует эквивалентной точке на цикле синусоидального сигнала. Число точек на окружности определяется разрядностью фазового аккумулятора (А). Фазовый вектор «вращается» с равномерной скоростью, каждый цикл оборота вектора соответствует полному периоду гармонического сигнала. Выход фазового аккумулятора представляет собой линейную периодическую функцию и может быть использован для непосредственной генерации пилообразного сигнала (если подать на вход ЦАП). Для того, чтобы получить гармонический сигнал выход аккумулятора следует использовать в качестве адреса для ПЗУ с таблицей синуса.

Выходной код аккумулятора фазы представляет собой код мгновенной фазы выходного сигнала. Постоянная добавка, которая используется при работе аккумулятора фазы, представляет собой приращение фазы за один такт работы устройства. Чем быстрее изменяется фаза во времени, тем больше частота генерируемого сигнала. Поэтому значение приращения фазы фактически является кодом выходной частоты. Аккумулятор фазы работает с периодическими переполнениями. Такое периодическое переполнение соответствует периодическому поведению функции синуса с периодом 2π. Другими словами, частота переполнений аккумулятора фазы равна частоте выходного сигнала. Эта частота определяется формулой:

(1)

(1)

где fout – выходная частота, fclk – тактовая частота, D – код частоты, A – разрядность аккумулятора фазы.

При изменении значения D частота на выходе синтезатора меняется сразу, и при этом сигнал не имеет разрывов. Здесь отсутствует переходный процесс захвата частоты, присущий генераторам с петлёй ФАПЧ.

Важным параметрами DDS является разрешающая способность по частоте ΔF:

(2)

(2)

Из этого соотношения следует еще одно уникальное свойство синтезатора частоты: если увеличить разрядность N, то уменьшится шаг перестройки частоты. Причем особых ограничений здесь нет. Например, если разрядность накапливающего сумматора 32 бита, а тактовая частота составляет 50 МГц, то частотное разрешение составит порядка 0,01 Гц! Для уменьшения объема ПЗУ можно использовать свойства симметрии функции синуса. В большинстве DDS в ПЗУ содержится только 1/4 периода. Правда, при этом немного усложняется логика формирования адреса.

Основные преимущества DDS:

- цифровое управление частотой и фазой выходного сигнала;

- очень высокое разрешение по частоте и фазе;

- экстремально быстрый переход на другую частоту (или фазу), перестройка по частоте без разрыва фазы, без выбросов и других аномалий, связанных с временем установления;

- цифровой интерфейс легко позволяет реализовать микроконтроллерное управление.

2.3 Усечение фазы

Усечение фазы является важным аспектом архитектуры DDS. Для примера рассмотрим DDS с 32-разрядным аккумулятором фазы. Для прямого преобразования 32 бит фазы в соответствующую амплитуду потребуется в ПЗУ хранить 232 отсчета синуса. Если положить, что каждый отсчет хранится с 8-разрядной точностью, то потребуется 4 гигабайта памяти.

Увеличение разрядности аккумулятора фазы не требует обязательного увеличения размера ПЗУ. Для адресации можно использовать лишь необходимое количество старших разрядов кода фазы. Например, в 32-разрядном DDS можно использовать только старшие 12 бит регистра фазы. В этом случае младшие 20 бит будут проигнорированы (усечены).

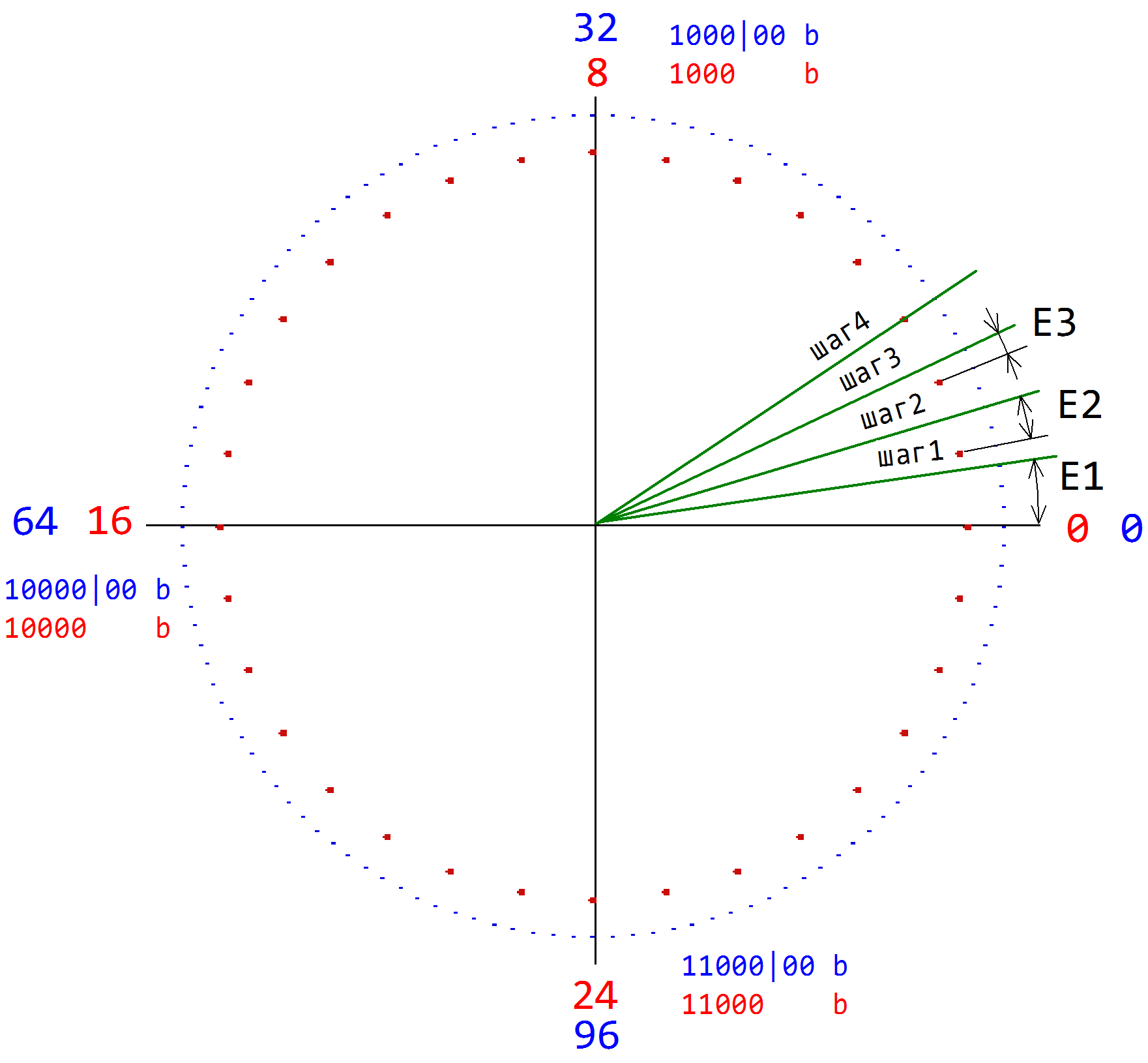

Для понимания последствий усечения фазы вернемся к круговой фазовой диаграмме. Рассмотрим простую архитектуру DDS, использующую 7-ми разрядный аккумулятор, в котором для адресации ПЗУ используются старшие 5 разрядов. На рисунке 4 изображена круговая фазовая диаграмма, синие точки показывают все возможные значения 7-ми битного регистра фазы (внешняя окружность), красные точки (внутренняя окружность) – значения после усечения – непосредственные адреса для ПЗУ. Полный период для аккумулятора фазы составляет 128 шагов, полный период для адресов ПЗУ составляет 32 шага.

Рисунок 4 – Круговая диаграмма. Ошибки усечения фазы

Для 7-ми битного аккумулятора разрешение фазы составит:

Разрешение после усечения:

На круговой диаграмме показаны первые четыре фазовых угла для кода частоты, равному 3 (то есть, аккумулятор считает с шагом 3). Обратите внимание, что первый шаг не дотягивает до первой метки внутреннего круга. Таким образом возникает расхождение между фазой аккумулятора (внешняя окружность) и фазой, определяемой усечением до 5-ти бит (внутренняя окружность). Это расхождение приводит к ошибке в 8.44 °.

Параметры ошибки четырех первых шагов аккумулятора приведены в Таблица 1.

Таблица 1 – Анализ ошибки усечении фазы

| Номер шага |

Аккумулятор |

Адрес ПЗУ |

Ошибка |

| Значение |

Угол |

Значение |

Угол |

| 1 |

3 |

8.44° |

0 |

0.00° |

8.44° |

| 2 |

6 |

16.88° |

1 |

11.25° |

5.63° |

| 3 |

9 |

25.31° |

2 |

22.50° |

2.81° |

| 4 |

12 |

33.75° |

3 |

33.75° |

0.00° |

Очевидно, что фазовые ошибки, вносимые усечением разрядности регистра аккумулятора, приведут к ошибкам амплитуды в процессе преобразования фазы в амплитуду. Независимо от выбранного кода частоты (шага аккумулятора) после достаточного количества оборотов фазового цикла фаза аккумулятора и фаза после усечения будут совпадать. В рассмотренном примере для этого понадобилось всего четыре шага. Поэтому эти ошибки являются периодическими. А так как эти ошибки периодические во временной области, то в на спектре сигнала они будут отображаться как отдельные линии (гармоники).

Уровень паразитных гармоник вызванных эффектом усечения зависит от трех факторов:

- разрядность аккумулятора фазы (А);

- разрядность фазы после усечения (P);

- значение кода частоты (D).

Очевидно, что при некоторых значениях кода частоты никакой ошибки не произойдет (для рассмотренного примера, это D = 4) и составляющие в спектре не появятся, в то же время для других значений D ошибка будет максимальной, а уровень паразитных гармоник будет наибольшим.

Если разность A-P больше или равно 4, что обычно выполняется на практике, то максимальный уровень паразитной гармоники (в дБ) относительно основной моды достаточно точно можно найти по формуле:

Lph = - 6.02 ·P (3)

где P-разрядность фазы после усечения.

Так для DDS с разрядностью аккумулятора 32 бита и разрядности фазы 12 бит, уровень паразитных гармоник не превысит -72 дБ.

Значение кода частоты (D) при котором наблюдается наибольший уровень паразитных гармоник можно определит по формуле:

НОД(D, 2A - P ) = 2A - P - 1 (4)

где НОД – наибольший общий делитель.

Для рассмотренного примера, где А = 7 и P = 5, максимальный уровень будет наблюдаться при:

НОД(D, 27 - 5) = 27 - 5 - 1,

НОД(D, 4) = 2.

То есть, D должен делиться без остатка на 2, но не делиться на 4. Этому, например, удовлетворяют значения 2, 6, 10, 14 …

Значение кода частоты (D), при котором составляющие отсутствуют:

НОД(D, 2A - P ) = 2A - P (5)

Другими словами, D должно быть кратно 2A - P. Для рассмотренного примера D должно делиться на 4 без остатка.

3 Введение в Verilog

3.2 Работа с блоком памяти в Verilog

В Verilog память – это массив регистров. Объявляется следующим образом:

reg [7:0] mem_name[1023:0]; // «mem_name» память, которая содержит 1024 ячеек,

// каждая ячейка состоит из 8-битного регистра.Доступ к отдельной ячейке осуществляется так:

dac1_d <= mem_name[124] // 8-ми битное значение из 124-ой ячейки

// записывается в 8-битный регистр dac1_dДоступ к отдельному биту ячейки осуществляется так:

assign led[0] <= mem_name[124][7] // Значение старшего (7-го) бита 124-ой ячейки

// назначается 0-му биту шины ledДоступ к группе бит ячейки осуществляется так:

assign led <= mem_name[124][7:4] // Значение четырех старших бит 124-ой ячейки

// назначается шине ledПамять может быть инициализирована начальными значениями с помощью системных функций readmemh и readmemb. При компиляции проекта функции считывают значение из текстового файла и помещают их в указанную память. Файл для функции readmemh должен содержать данные в шестнадцатеричном формате, для функции readmemb – в двоичном.

Вызов функций должен происходить в блоке инициализации Inicial.

Общий синтаксис вызова следующий:

$readmemh ( " file_name " , memory_name [ , start_addr [ , finish_addr ] ] );

где file_name – относительный путь к файлу и имя, memory_name – имя инициализируемой памяти, start_addr – начальный адрес для загрузки, finish_addr – конечный адрес. Последние два параметра опциональны.

Рассмотрим пример использования. Объявим память:

reg [7:0] mem[0:255]; // 256 8-битных ячеек

Учитывая это объявление, каждый из следующих операторов загружает данные в mem по-разному:

initial $readmemh("mem.mif", mem);

initial $readmemh("mem.mif ", mem, 16);

initial $readmemh("mem.mif ", mem, 128, 1);Подразумевается, что файл mem.mif содержит 256 значений. Первый оператор загружает всю доступную память начиная с нулевого адреса. Второй оператор начинает загружать память с 16 адреса и продолжает до адреса 255. Третий оператор начинает загрузку с 128-го адреса и завершает адресом 1.

3.1 Поведенческий блок always@

Поведенческий блок always@ предназначен для описания событий, которые должны произойти при определенных условиях. Блок начинается с ключевого слова always, затем следует набор параметров (событий, «список чувствительности») в круглых скобках, далее, как правило следует ключевое слово begin, набор операций и ключевое слово end:

// <edge_events> может содержать любое число событий posedge или negedge

// разделенных через ключевое слово "or", например:

// always@(posedge clk or negedge reset)

always@(<edge_events>)

begin

// Различные операции, программный код

endПрограммный код внутри блока срабатывает когда происходит событие из списка. В качестве события может выступать положительный (нарастающий) либо отрицательный (спадающий) фронт сигнала. Для задания положительного фронта используется ключевое слово posedge – от английского «positive edge», для отрицательного фронта – ключевое слово negedge – «negative edge».

Конструкция always @(posedge Clock) и always @(negedge Clock) используются для описания синхронных схем, например, регистров.

На листинге ниже каждый такт на линии clk_pll в регистр dac1_d записывается значение из переменной (может быть регистр или шина) var.

// Следует читать так:

always @(posedge clk_pll) // Для каждого положительно фронта на линии clk_pll

begin // выполнить код:

dac1_d <= var;

end // Конец выполняемого кода3.3 Привязка портов модуля к выводам ПЛИС

Существенно ускорить создание проекта в Quartus можно выполнив назначение портов модуля на выводы ПЛИС непосредственно в текстовом файле модуля. Для этого при объявлении портов модуля верхнего уровня можно использовать атрибут синтеза chip_pin.

В языке Verilog HDL любые атрибуты синтеза размещают между разделителями (* и *). Атрибут chip_pin в следует указать в той же строке, что и объявление порта, которому назначаются контакты. Значение атрибута chip_pin должно быть строкой, содержащей список имен выводов устройства, разделенных запятыми.

В лабораторной работе используются заранее подготовленные файлы инициализации памяти. Используя Таблицу 3 следует выбрать файл для своего варианта и прописать его в инициализации ПЗУ.

Создать модуль pll для генерации тактовой частоты ЦАП, для этого использовать IP-функцию ALTPLL. Выходную частоту выбрать 100 кГц.

Скомпилировать проект. В Pin Planer проверить назначение выводов ПЛИС.

Используя утилиту LabForProg, загрузить конфигурационный *.rbf файл в ПЛИС учебного стенда LESO7.

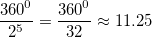

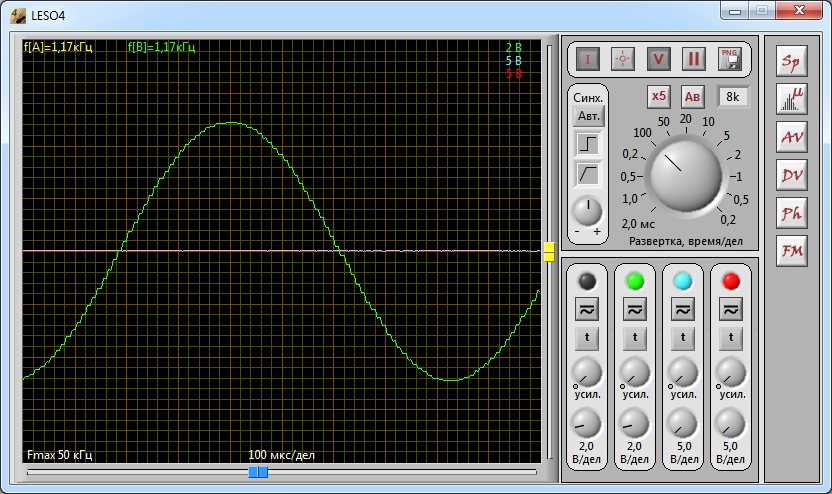

К второму и первому выходу ЦАП подключить входы анализатора сигналов LESO4. Выбор входов произвольный. Здесь и далее в примерах осциллограмм выход 1 ЦАП подключен к каналу А (желтый трек), выход 2 ЦАП подключен к каналу B (зеленый трек) (рисунок 5).

Рисунок 5 – Осциллограмма сигнала. Желтый канал – аккумулятор фазы, зеленый – гармонический сигнал

Сохранить осциллограмму (фаза и синус) и спектр сигнала (только синус).

4.1.2 Исследовать разрешающую способность по частоте DDS

Рассчитать шаг изменения частоты для текущих параметров DDS.

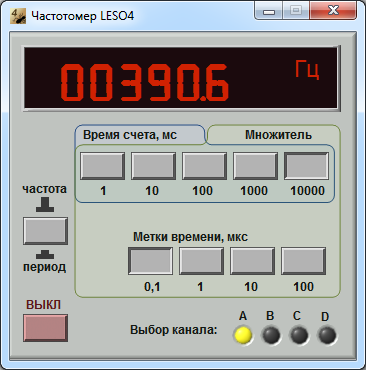

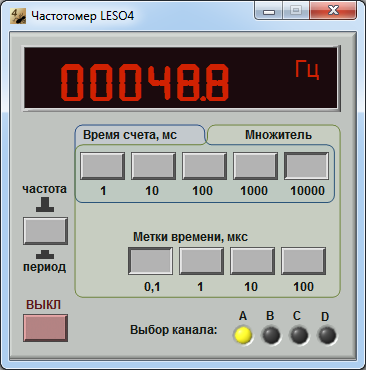

Экспериментально измерить шаг перестройки частоты. Для этого установить минимальную частоту генерации и с помощью частотомера LESO4 измерить частоту сигнала на выходе ЦАП (рисунок 6).

Рисунок 6 – Измерение шага перестройки частоты

Частотомер запускается из панели инструментов LESO4 кнопкой «FM»  . Для увеличения точности измерения рекомендуется поставить максимальное время счета.

. Для увеличения точности измерения рекомендуется поставить максимальное время счета.

Сохранить скриншот измерения.

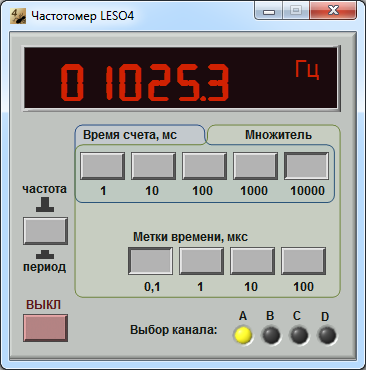

4.1.3 Генерация сигнала заданной частоты

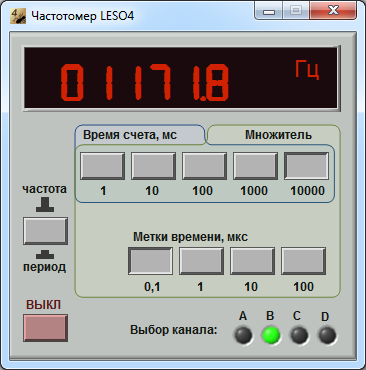

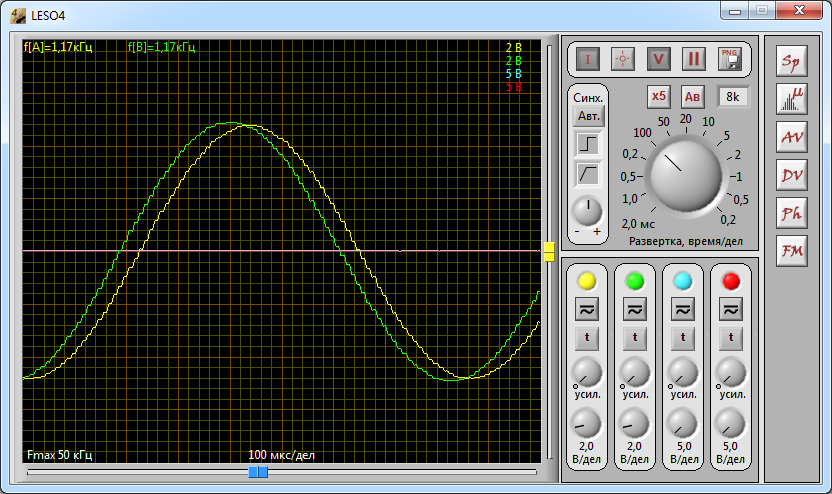

Рассчитать код частоты для получения гармонического сигнала с частотой согласно варианту. Экспериментально измерить полученную частоту сигнала. На рисунках ниже осциллограмма и измерение частоты сигнала с расчетной частотой 1 кГц.

Рисунок 7 – Сигнал с заданной частотой. Осциллограмма

Рисунок 8 – Измерение частоты сигнала. Расчетные 1000 Гц

Оценить погрешность установки частоты сигнала.

Сохранить осциллограмму сигнала и скриншот измерения частоты.

4.1.4 Исследовать разрешающую способность DDS по начальной фазе

Рассчитать шаг регулировки начальной фазы сигнала для текущих параметров DDS.

На оба канала ЦАП вывести сигнал с DDS. Установить для каждого канала одинаковую частоту согласно варианту. Первый канал считаем опорным, ко второму добавляем минимальное смещение фазы.

Для этого модифицируем поведенческий блок always следующим образом:

always @(posedge clk_pll)

begin

// На ЦАП1 выводим значение сигнала:

dac1_d <= {rom_1[phase_acc_1[7:0]], 6'h0};

// На ЦАП2 выводим значение сигнала со сдвигом фазы:

dac2_d <= {rom_1[phase_acc_1[7:0] +1], 6'h0};

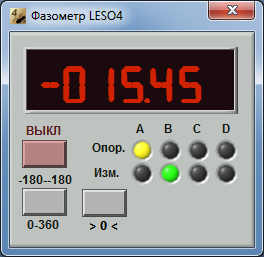

endС помощью фазометра LESO4 произвести измерение фазового сдвига. Фазометр запускается из панелей инструментов LESO4 кнопкой «Ph»  .

.

Особенность работы фазометра предполагает калибровку измерителя. Для этого на оба канала анализатора следует подать синхронный сигнал (сдвиг фаз отсутствует) и нажать кнопку «Установка нуля» (« >0< »). После этого можно подавать сигналы со сдвигом фаз (рисунок 9).

Рисунок 9 – Фазометр LESO4

Сохранить осциллограмму сигнала и скриншот измерения фазы.

4.1.5 Генерация сигнала с заданным фазовым сдвигом

Рассчитать код начальной фазы для получения гармонических сигналов с частотой и фазовым сдвигом согласно варианту. Экспериментально измерить полученный фазовый сдвиг. Сохранить осциллограммы сигналов (рисунок 10) и скриншот измерения фазы (рисунок 11).

Рисунок 10 – Сигналы со сдвигом фазы

Рисунок 11 – Измерение сдвига фазы

4.2 Этап 2. Увеличение разрядности фазы аккумулятора

4.2.1 Расчет

Рассчитать требуемую разрядность аккумулятора фазы для получения точности перестройки частоты не хуже заданной вариантом (таблица 2). Рассчитать шаг перестройки частоты и начальной фазы с учетом увеличенной разрядности аккумулятора.

4.2.2 Модернизировать модуль DDS

Изменить разрядность регистра фазы согласно результату расчета.

При изменении начальной фазы значение шага должно добавляться к регистру фазы до усечения, поэтому целесообразно ввести дополнительные сигналы, в которых будет храниться модифицированное значение фазы.

Для адресации ПЗУ использовать только старшие разряды регистра фазы. Ниже на листинге показана модифицированная часть модуля (в примере разрядности ЦАП: 8 бит, фазовый аккумулятор: 11 бит, размер таблицы: 256, код частоты и начальной фазы произвольный) :

4.2.3 Экспериментально измерить шаг перестройки частоты

Для этого установить минимальную частоту генерации и с помощью частотомера LESO4 измерить частоту сигнала на выходе ЦАП (рисунок 12).

Рисунок 12 – Измерение шага перестройки частоты

Сохранить скриншот измерения.

4.2.4 Генерация сигнала заданной частоты

Рассчитать код частоты для получения гармонического сигнала с частотой согласно варианту (Таблица 2). Экспериментально измерить полученную частоту сигнала.

Сохранить скриншот измерения.

Рисунок 13 – Измерение частоты сигнала. Расчетные 1000 Гц

4.2.5 Исследовать разрешающую способность DDS по начальной фазе

Рассчитать шаг регулировки начальной фазы сигнала для текущих параметров DDS.

На оба канала ЦАП вывести сигнал с DDS. Установить для каждого канала одинаковую частоту согласно варианту (таблица 2). Первый канал считаем опорным, ко второму добавляем смещение фазы.

При высокой разрядности фазового аккумулятора значение шага перестройки фазы может оказаться ниже чувствительности фазометра (0.2 °). В этом случае имеет смысл прибавлять 100 шагов, измерять сдвиг фаз и вычислять значение фазового сдвига, приходящееся на 1 шаг.

Особенность работы фазометра предполагает калибровку измерителя. Для этого на оба канала анализатора следует подать синхронный сигнал (сдвиг фаз отсутствует) и нажать кнопку «Установка нуля» (« >0< »). После этого можно подавать сигналы со сдвигом фаз (рисунок 14).

Рисунок 14 – Измерение фазы

В примере на рисунке выше сдвиг фазы на 100 шагов привело к разности фаз в 17.57 °, это значит, что на 1 шаг регулирования приходится 0.176 °.

Результаты расчетов и скриншот фазометра включить в отчет.

4.2.6 Генерация сигнала с заданным фазовым сдвигом

Рассчитать код начальной фазы для получения гармонических сигналов с частотой и фазовым сдвигом согласно варианту (таблица 2). Экспериментально измерить полученный фазовый сдвиг. Сохранить осциллограммы сигналов и скриншот измерения фазы (рисунок 15).

Рисунок 15 – Измерение фазы. Расчетное значение 15 °

4.3 Этап 3. Исследование эффекта усечения фазы

4.3.1 Предварительный расчет

В работе сравнивается уровень паразитных гармоник сигнала DDS с разрядностью фазы (P) 6 бит, 7 бит, 8 бит, вызванных эффектом усечения фазы. Для того, чтобы уменьшить влияние гармоник, вызванных квантованием сигнала рекомендуется установить эквивалентную разрядность ЦАП 8 бит, для этого при инициализации ПЗУ выбирать соответствующий файл с таблицей синуса (таблица 3).

Рассчитать для каждого значения P значение кода частоты при котором уровень паразитной составляющей будет максимальным (DmaxL) и минимальным (DminL). Использовать вычисленную в предыдущем пункте разрядность фазового аккумулятора.

Рассчитать для каждого значения P ожидаемый максимальный относительный уровень паразитной гармоники  .

.

Результаты расчетов занести в таблица 4.

Таблица 4 – Исследование паразитных гармоник. Расчет и измерение

| Разрядность фазы (P) |

Расчет |

Измерение |

| DmaxL |

DminL |

Lph, дБ |

Lph при DmaxL |

Lph при DminL |

| 6 |

|

|

|

|

|

| 7 |

|

|

|

|

|

| 8 |

|

|

|

|

|

Пример расчета. Разрядность фазового аккумулятора A = 11, разрядность фазы после усечения P = 6.

По формуле 4 находим что для DmazL должно выполняться:

НОД(DmaxL, 211 - 6) = 211 - 6 - 1,

НОД(DmaxL, 32) = 16.

Следовательно DmaxL можно получить умножив 16 на любое простое число за исключением двойки, например 5. Выбираем DmaxL = 80.

По формуле 5 находим что для DminL должно выполняться:

НОД(DminL, 211 - 6) = 211 - 6,

НОД(DminL, 32) = 32.

То есть DminL должно быть кратно 32. Выбираем DminL = 96.

Максимальный уровень паразитной гармоники вычисляем по формуле 3:

Lph = - 6.02 · 6 = -36.12.

4.3.2 Экспериментальное исследование

Модифицировать модуль DDS согласно заданию. При исследовании сигнала с различными D удобно в программу ввести два фазовых аккумулятора, для одного шаг выбрать DmaxL, для второго выбрать DminL.

Скомпилировать проект. Файл конфигурации загрузить в ПЛИС учебного стенда.

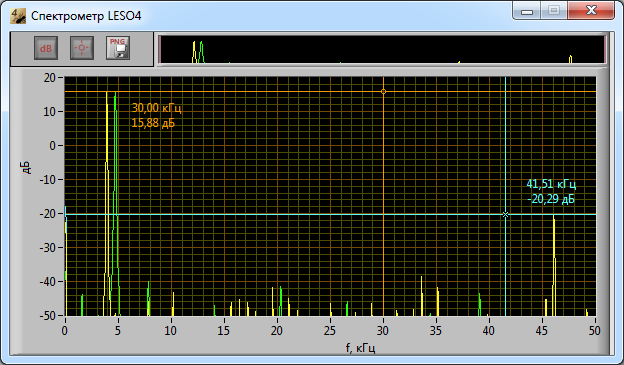

Измерить максимальный уровень паразитных составляющих для сигнала с кодом DmaxL и DminL .

При спектральных измерениях значение развертки следует выбрать таким образом, чтобы диапазон частот на графике спектра соответствовал половине частоты дискретизации ЦАП (частота pll).

При измерении уровня составляющих спектра удобно использовать курсоры (активируются кнопкой  ). Перемещать курсоры можно мышью.

). Перемещать курсоры можно мышью.

При измерении может понадобится изменить масштаб графика по вертикали, для этого можно непосредственно задать минимальное и максимальное значение шкалы (щелчок по значению мышью, ввод с клавиатуры).

Если компоненты двух сигналов накладываются друг на друга и затрудняют измерение, то можно временно отключить отображение спектра мешающего канала в контекстном меню графика (щелчок правой кнопкой мыши по графику).

При измерении относительного уровня составляющей нужно помнить, что измерение происходит относительно уровня основной гармоники. Для вычисления относительного уровня следует из уровня основной гармоники вычесть уровень измеряемой компоненты.

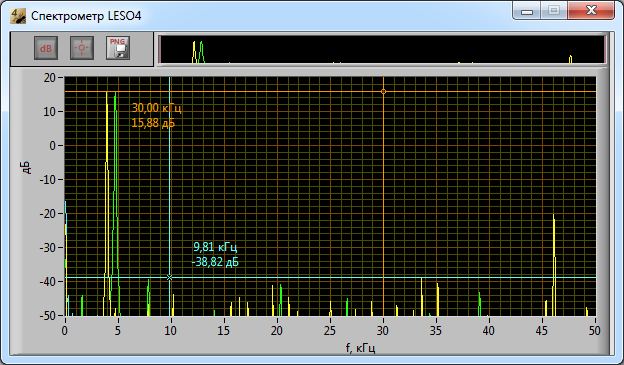

На рисунке 16 и рисунке 17 показан спектр сигналов для DDS из примера выше.

Рисунок 16 – Измерение уровня паразитных составляющих Lph при DmaxL

Рисунок 17 – Измерение уровня паразитных составляющих Lph при DminL

Из рисунке 16 следует, что для первого сигнала максимальный уровень паразитных гармоник составляет -36.17 дБ, а из рисунка 17 следует, что для второго сигнала уровень гармоник не превышает -54.7 дБ.

Для каждого значения P повторить измерение. Результат занести в таблицу 4.

Сохранить скриншоты измерения спектров сигналов.

5 Вопросы для самопроверки:

- С чем связана погрешность регулировки частоты сигнала. Какие параметры влияют на это.

- С чем связана погрешность регулировки начальной фазы сигнала, какие параметры влияют на это.

- Почему при сдвиге начальной фазы значение сдвига нужно добавлять до усечения?

- Почему уровень паразитных гармоник в сигнале зависит от кода частоты?

- Какие факторы определяют уровень паразитных гармоник в спектре сигнала DDS, каким образом?

- При каких значениях разрядности ЦАП наращивать разрядность фазы теряет смысл?

- Каким образом с помощью DDS получить сигналы прямоугольной, треугольной и пилообразной формы?

6 Содержание отчета:

- Название и цель работы.

- Функциональная схема DDS.

- Предварительный расчета (для пунктов, где он выполняется).

- Осциллограммы и скриншоты измерений (для пунктов, где это указано).

- Таблица исследования паразитных гармоник.

- Для каждого этапа сделать выводы.